## LM1972

### μPot™ 2 チャネル 78dB オーディオアッテネータ (ミュート機能付き)

#### 概要

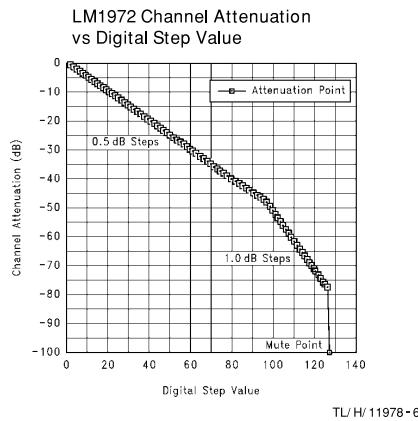

LM1972 は、デジタル制御型 2 チャネル・78dB の CMOS オーディオ・アッテネータです。各チャネルは、0dB ~ 47.5dB の範囲で 0.5dB ステップ、48dB ~ 78dB 範囲で 1.0dB ステップの減衰が可能であり、減衰量 104dB のミュート機能も内蔵しています。この対数減衰ステップは、アプリケーションに合わせてソフトウェアにより調整することができます。

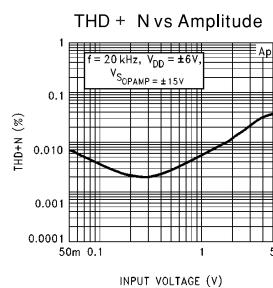

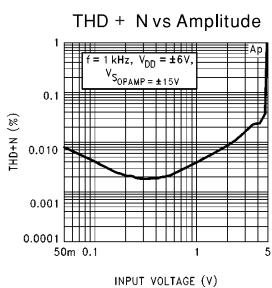

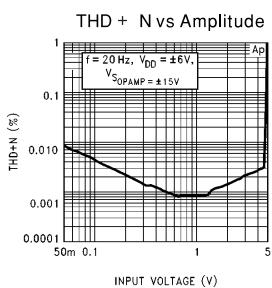

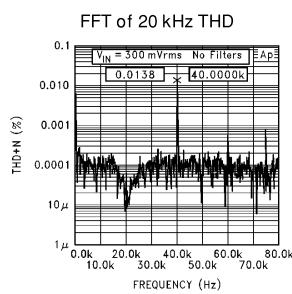

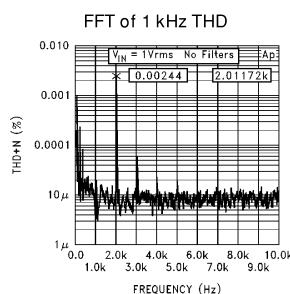

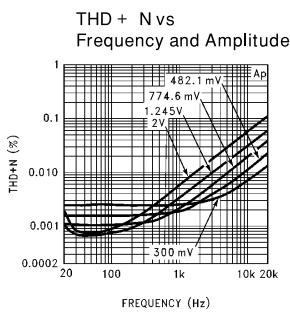

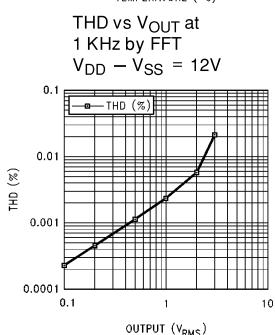

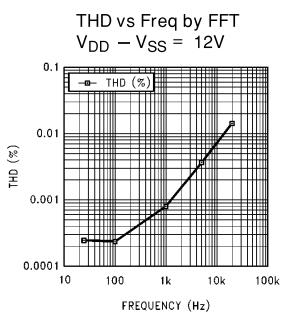

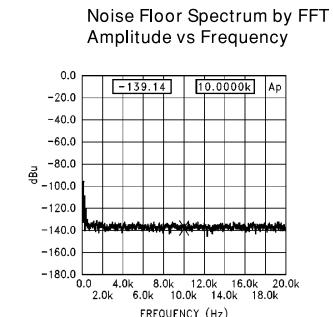

μPot の性能は、その優れた S/N 比、極めて低い全高調波歪み + ノイズ (THD + N) そして、高精度のチャネル・セバレーション特性により実証されています。μPot は、入力信号を出力信号から分離するミュート機能を備え、96dB 以上の減衰量が得られます。また、減衰量の設定を変更してもポップ音が生じることはありません。

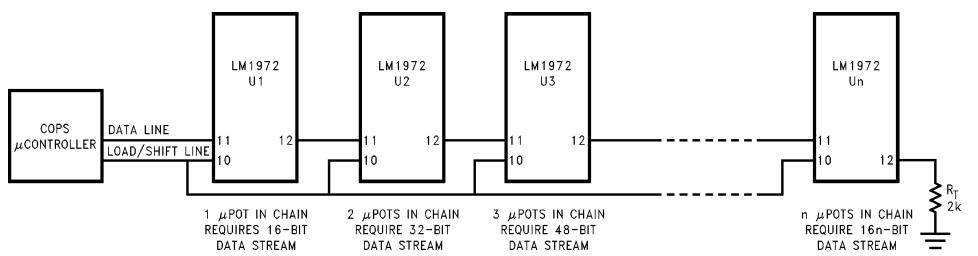

LM1972 は TTL/CMOS コンパチブルの 3 線シリアル・インターフェースを介し、チャネル選択用と減衰レベル設定用のデータを受信します。内蔵のデータ出力ピンを介して複数の μPot をデジ털接続することにより、アプリケーションに合わせてイネーブル・ライン / データ・ライン数を削減することができます。

#### 主な仕様

|                  |                    |

|------------------|--------------------|

| 全高調波歪み + ノイズ     | 0.003 % (最大)       |

| 周波数特性            | 100kHz (-3dB) (最小) |

| 減衰範囲(ミュートを除く)    | 78dB (代表値)         |

| 減衰誤差             | ± 0.25dB (最大)      |

| SN 比 (4VRms を基準) | 110dB (最小)         |

| チャネル・セバレーション     | 100dB (最小)         |

#### 特長

- 3 線シリアル・インターフェース

- デジタル接続が可能

- 減衰量 104dB のミュート機能

- 減衰量変更によるポップ / クリック音を生じない

#### アプリケーション

- スタジオ用自動ミキシング・コンソール

- 音楽再生システム

- 音響効果システム

- 電子音楽 (MIDI)

- パーソナル・コンピュータによるオーディオ制御

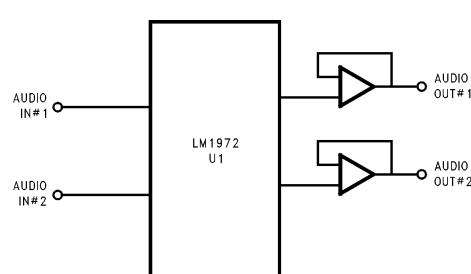

#### Typical Application

TL/H/11978-1

FIGURE 1. Typical Audio Attenuator Application Circuit

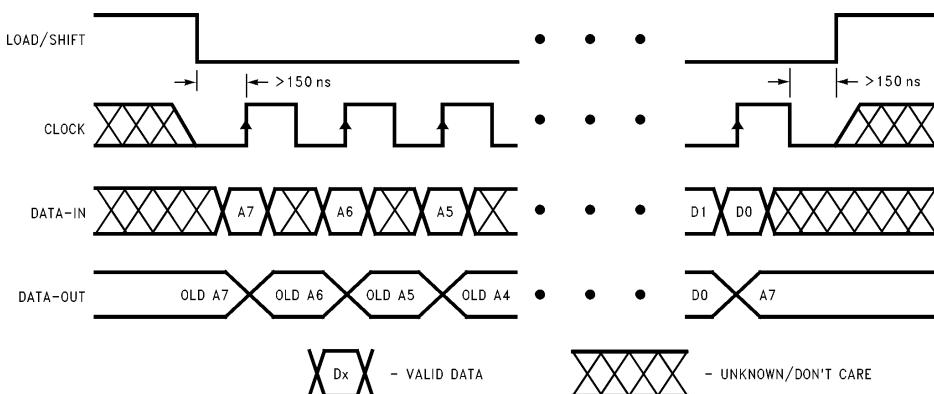

#### Connection Diagram

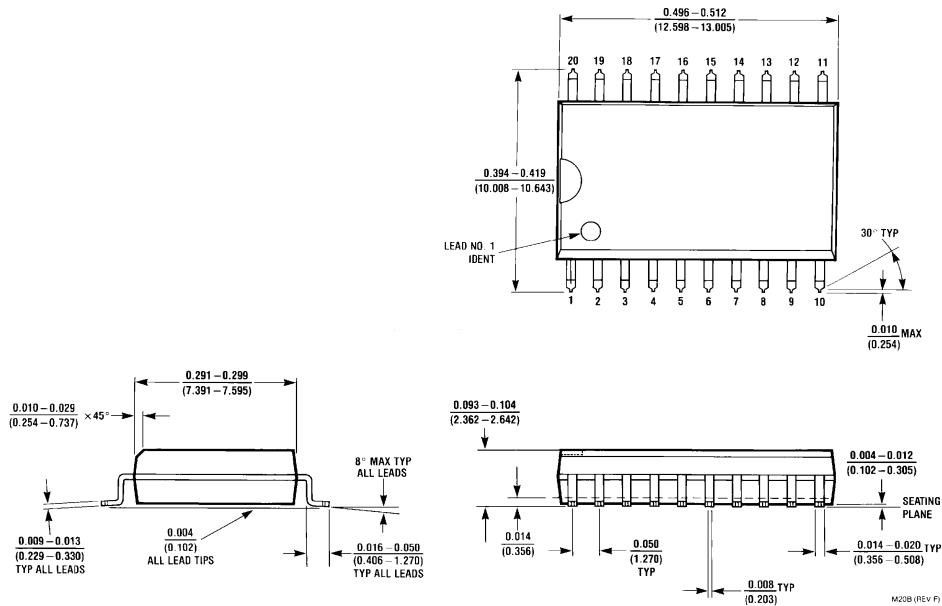

Top View

Order Number LM1972M or LM1972N

See NS Package Number M20B or N20A

μPot™ および Overture™ はナショナルセミコンダクター社の商標です。

## 絶対最大定格 (Note 1, 2)

本データシートには軍用・航空宇宙用の規格は記載されていません。

関連する電気的信頼性試験方法の規格を参照下さい。

|                            |                                    |

|----------------------------|------------------------------------|

| 電源電圧 ( $V_{DD} - V_{SS}$ ) | 15V                                |

| 全てのピン電圧                    | $V_{SS} - 0.2V \sim V_{DD} + 0.2V$ |

| 消費電力 (Note 3)              | 150mW                              |

| ESD 耐圧 (Note 4)            | 2000V                              |

| 接合部温度                      | 150                                |

| ハンダ付け条件                    |                                    |

| Nパッケージ(10秒)                | + 260                              |

| 保存温度範囲                     | - 65 ~ + 150                       |

## 動作条件 (Note 1, 2)

|                            |           |       |           |      |            |

|----------------------------|-----------|-------|-----------|------|------------|

| 温度範囲                       | $T_{MIN}$ | $T_A$ | $T_{MAX}$ | 0    | $T_A + 70$ |

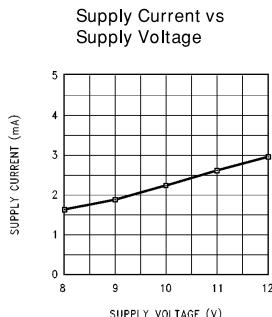

| 電源電圧 ( $V_{DD} - V_{SS}$ ) |           |       |           | 4.5V | ~ 12V      |

## 電気的特性 (Note 1, 2)

特記のない限り、以下の規格値は  $V_{DD} = + 6V$ ,  $V_{SS} = - 6V$ ,  $V_{IN} = 5.5V_{pk}$ ,  $f = 1kHz$  の条件で全チャネルに対して適用されます。リミット値は  $T_A = + 25$  に対して適用され、デジタル入力は TTL/CMOS コンバチブルです。

| Symbol | Parameter                                     | Conditions                                                                                                    | LM1972                               |                                     | Units<br>(Limits)                                        |

|--------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------|----------------------------------------------------------|

|        |                                               |                                                                                                               | Typical<br>(Note 5)                  | Limit<br>(Note 6)                   |                                                          |

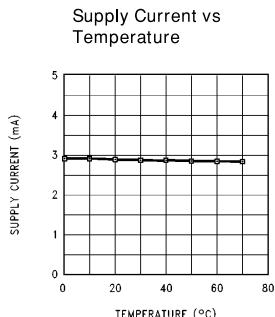

| $I_S$  | Supply Current                                | Inputs are AC Grounded                                                                                        | 2                                    | 4                                   | mA (max)                                                 |

| THD+N  | Total Harmonic Distortion plus Noise          | $V_{IN} = 0.5 V_{pk}$ @ 0dB Attenuation                                                                       | 0.0008                               | 0.003                               | % (max)                                                  |

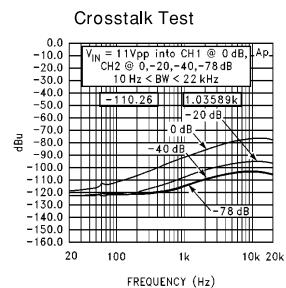

| XTalk  | Crosstalk (Channel Separation)                | 0dB Attenuation for $V_{IN}$<br>$V_{CH}$ measured @ -78dB                                                     | 110                                  | 100                                 | dB (min)                                                 |

| SNR    | Signal-to-Noise Ratio                         | Inputs are AC Grounded<br>@ -12dB Attenuation<br>A-Weighted                                                   | 120                                  | 110                                 | dB (min)                                                 |

| $A_M$  | Mute Attenuation                              |                                                                                                               | 104                                  | 96                                  | dB (min)                                                 |

|        | Attenuation Step Size Error                   | 0dB to -47.5dB<br>-48dB to -78dB                                                                              |                                      | $\pm 0.05$<br>$\pm 0.25$            | dB (max)<br>dB (max)                                     |

|        | Absolute Attenuation Error                    | Attenuation @ 0dB<br>Attenuation @ -20dB<br>Attenuation @ -40dB<br>Attenuation @ -60dB<br>Attenuation @ -78dB | 0.03<br>19.8<br>39.5<br>59.3<br>76.3 | 0.5<br>19.0<br>39.0<br>57.5<br>74.5 | dB (min)<br>dB (min)<br>dB (min)<br>dB (min)<br>dB (min) |

|        | Channel-to-Channel Attenuation Tracking Error | Attenuation @ 0dB, -20dB, -40dB, -60dB<br>Attenuation @ -78dB                                                 |                                      | $\pm 0.5$<br>$\pm 0.75$             | dB (max)<br>dB (max)                                     |

|        | $I_{LEAK}$                                    | Analog Input Leakage Current                                                                                  | Inputs are AC Grounded               | 10.0                                | 100 nA (max)                                             |

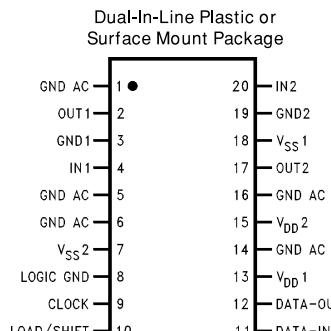

FIGURE 2. Timing Diagram

TLH/11978-3

## 電気的特性 (Note 1、2)(つづき)

特記のない限り、以下の規格値は  $V_{DD} = + 6V$ 、 $V_{SS} = - 6V$ 、 $V_{IN} = 5.5Vpk$ 、 $f = 1kHz$  の条件で全チャネルに対して適用されます。リミット値は  $T_A = + 25^\circ C$  に対して適用され、デジタル入力は TTL/CMOS コンバチブルです。

| Symbol    | Parameter                | Conditions                                   | LM1972              |                   | Units<br>(Limits)    |

|-----------|--------------------------|----------------------------------------------|---------------------|-------------------|----------------------|

|           |                          |                                              | Typical<br>(Note 5) | Limit<br>(Note 6) |                      |

| $R_{IN}$  | AC Input Impedance       | Pins 4, 20, $V_{IN} = 1.0 Vpk$ , $f = 1 kHz$ | 40                  | 20<br>60          | kΩ (min)<br>kΩ (max) |

| $I_{IN}$  | Input Current            | @ Pins 9, 10, 11 @ $0V < V_{IN} < 5V$        | 1.0                 | ± 100             | nA (max)             |

| $f_{CLK}$ | Clock Frequency          |                                              | 3                   | 2                 | MHz (max)            |

| $V_{IH}$  | High-Level Input Voltage | @ Pins 9, 10, 11                             |                     | 2.0               | V (min)              |

| $V_{IL}$  | Low-Level Input Voltage  | @ Pins 9, 10, 11                             |                     | 0.8               | V (max)              |

|           | Data-Out Levels (Pin 12) | $V_{DD} = 6V$ , $V_{SS} = 0V$                |                     | 0.1<br>5.9        | V (max)<br>V (min)   |

Note 1: 特記のない限り、全電圧は GND 端子(1、3、5、6、14、16、19)を基準にして測定されます。

Note 2: 「絶対最大定格」とは、デバイスに破壊が発生する可能性のあるリミット値をいいます。「動作条件」とはデバイスが機能する条件を示しますが、特定の性能リミット値を保証するものではありません。「電気的特性」とは、特定の性能リミット値を保証する特別な試験条件での AC および DC の電気的仕様を示します。この場合、デバイスが「動作条件」の範囲にあるものとします。リミット値(Limit)が記載されていないパラメータの仕様は保証されませんが、代表値(Typical)はデバイス性能を示す目安になります。

Note 3: 温度上昇時の動作では、最大消費電力の定格を  $T_{JMAX}$  (最大接合部温度)  $\theta_{JA}$  (接合部・周囲温度間熱抵抗) および  $T_A$  (周囲温度) に従って下げなければなりません。最大許容消費電力は  $PD = (T_{JMAX} - T_A)\theta_{JA}$ 、または絶対最大定格で示される値のうち、いずれか低い方の値です。LM1972 の場合、 $T_{JMAX}$  は + 150°C 、基板実装における  $\theta_{JA}$  は 65 °C/W です。

Note 4: 使用した試験回路は、人体モデルに基づき、直列抵抗 1.5kΩ と 100pF のコンデンサから成る回路を使用し各端子に放電させます。

Note 5: 代表値(Typical)は、 $T_A = + 25^\circ C$  で得られる最も標準的な値です。

Note 6: リミット値(Limit)は、ナショナルセミコンダクター社の AOQL (平均出荷品質レベル)に基づき保証されます。

## 端子説明

信号グランド(3、19):各入力専用の独立したグランド(GND1、GND2)

信号入力(4、20):2つの独立した信号入力ピン(IN1、IN2)

信号出力(2、17):2つの独立した信号出力ピン(OUT1、OUT2)

電源(13、15):正電源ピン(V<sub>DD1</sub>、V<sub>DD2</sub>)

電源(7、18):負電源ピン(V<sub>SS1</sub>、V<sub>SS2</sub>) 単一電源構成の場合はグランドに接続。

AC グランド(1、5、6、14、16):ダイに接続されていない(ワイヤボンディングされていない)ピン。隣接ピン間における信号のクロストークを防ぐために、これらのピンのAC 接地が必要です。例えば、ピン14をピン13、ピン15にテカッピングすることで、配線が容易になり最良の信号絶縁が行えます。

ロジック・グランド(8):インターフェース・ライン(クロック、ロード/シフト、データ入力、データ出力)用のデジタル信号グランド。

クロック(9):TTL/CMOS レベル・コンパチブルのクロック入力ピン。入力クロックの立ち上がりエッジで、このピンからデータが内部のシフトレジスタにロードされます。

ロード/シフト(10):TTL/CMOS レベル・コンパチブルのロード/シフト入力ピン。デバイスのイネーブル・ピンとして働き、この入力がLow レベル(0V)の間、クロックに同期してデータが取り込まれます。

データ入力(11):TTL/CMOS レベル・コンパチブルのデータ入力ピン。マイクロ・コントローラからのシリアル・データはこのピンを介して取り込まれ、チャネルの減衰レベルを変更するためにラッチ/デコードされます。

データ出力(12):同一データ・ラインで複数のμPot を制御するデイジーチェーン・モード用ピン。マイクロ・コントローラからデイジーチェーンにデータが入力されると、シフトレジスタ内の先行データはデータ出力ピンからチェーンの次段μPot にシフトアウトされます(チェーンの最終μPot であればグランドにシフトアウト)。ロード/シフト・ラインは、新しいデータがすべて個々のレジスタにシフトインした後にHigh にセットします。

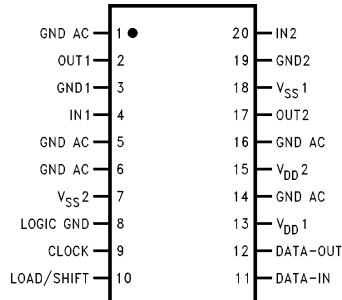

## Connection Diagram

TL/H/11978-4

## Typical Performance Characteristics

TL/H/1197B-5

## アプリケーション情報

### 減衰ステップの構成

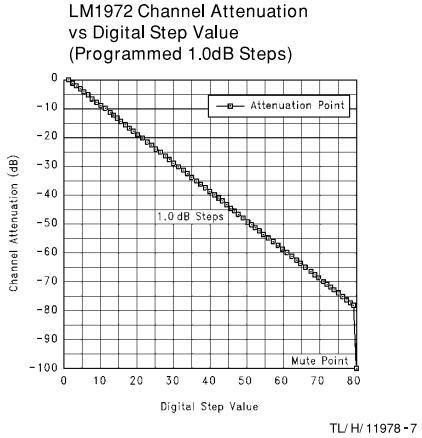

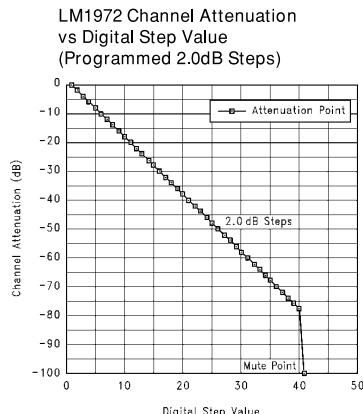

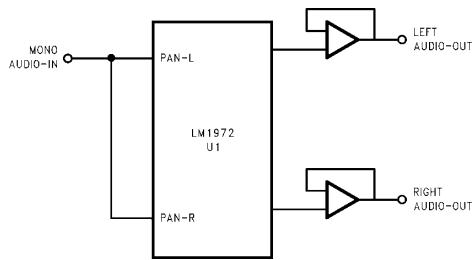

Fig. 3 に LM1972 $\mu$ Pot の基本的な減衰ステップ特性曲線を示します。この減衰ステップは、アプリケーションに応じてソフトウェアで変更できます。例えば、Fig. 4 に示すように、1dB 刻みの一定したステップ幅で対数的に減衰を行うことも可能です。減衰ステップをカスタマイズするうえで、各減衰レベル (dB) とデータ・ビット値を対応させることが必要となります (Table 1 参照)。デバイスの減衰レベルは、チャネル・アドレスが認識された場合に限り変更されます。チャネル・アドレスが認識されると、Table 1 のデータ・ビットに対応する減衰レベルに変更されます。LM1972 は、モノラル信号を左右のチャネルに分離するパンニング制御回路として構成することもできます (Fig. 6 参照)。この回路では LM1972 の基本的な減衰ステップを用いるか、Fig. 4 に示すように 1dB の一定したステップ幅で対数減衰を行うようにプログラムすることも可能です。

FIGURE 3. LM1972 Attenuation Step Scheme

FIGURE 4. LM1972 1.0dB Attenuation Step Scheme

FIGURE 5. LM1972 2.0dB Attenuation Step Scheme

FIGURE 6. Mono Panning Circuit

### 入力インピーダンス

$\mu$ Pot の入力インピーダンスは、40k $\Omega$  (標準) で一定です。通常、不要な DC 成分がデバイス内に伝播するのを防ぐために、1 $\mu$ F の入力カッピング・コンデンサを付加しますが、前段の DC オフセットが無視できる程度であれば、このコンデンサは必要ありません。ただし、高性能システムの場合は、入力カッピング・コンデンサの使用を推奨します。

### 出力インピーダンス

$\mu$ Pot の出力インピーダンスは通常、25k $\Omega$  ~ 35k $\Omega$  の範囲で減衰ステップの変化とともに非線形的に変化します。これは、 $\mu$ Pot が対数的な減衰特性をもつ抵抗ラダー・ネットワーク回路から構成されているためです。したがって、 $\mu$ Pot は線形的なポテンショメータとしてはなく、対数アッテネータとしてみなすことができます。

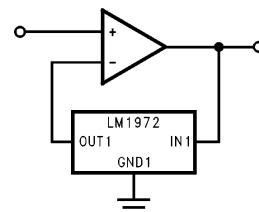

$\mu$ Pot の直線性の測定にはバッファが必要です。これは、ほとんどの測定システムの場合、入力インピーダンスが高くなく、必要な測定精度が得られないためです。測定システムの入力インピーダンスが低いと、 $\mu$ Pot の出力に負荷がかかり、測定結果は不正確になります。こうした負荷の影響を防ぐために、バッファ / アンプとして JFET 入力オペアンプを使用して下さい。この場合、 $\mu$ Pot の性能は、外付けのバッファ / アンプの性能にのみ影響されます。

## アプリケーション情報(つづき)

### ミュート機能

$\mu$ Pot の大きな特長の一つは、入力信号を 104dB 減衰するミュート機能を内蔵していることです (Fig. 3 参照)。これは、出力を入力から物理的に切り離すとともに、約 2k $\Omega$  の抵抗を介して出力ピンを接地することで実現しています。

ミュート機能は、デバイスの電源投入時に、または、0111 1111 ~ 1111 1111までのバイナリ・データがデバイスにシリアル転送された時に実行されます。これらのバイナリ・データが送られると、デバイスはそれまで設定されていた減衰動作からミュート動作に移行します。したがって、ミュート・ボタンをシステムに装備すれば、そのボタンを押すことにより、マイクロ・コントローラから  $\mu$ Pot に該当データを送り、一方のチャネルまたは両チャネルをミュートさせることができます。この機能はソフトウェアで行うため、システム構成において大幅な柔軟性が得られます。

### DC 入力

$\mu$ Pot はオーディオ帯域信号用のアッテネータとして設計されていますが、入力 DC 電圧のトラッキングも可能です。このデバイスでは、各電源電圧から 1 ダイオード・ドロップ分までの DC 電圧をトラッキングすることができます。

$\mu$ Pot の出力段にバッファを用いた場合、DC トラッキングの能力は  $\mu$ Pot の出力バッファのゲインと電源電圧によって決まるに注意して下さい。さらに、出力バッファの電源電圧は  $\mu$ Pot の電源電圧と同じにする必要がなく、電源電圧を上げて DC トラッキングの能力を高めることも可能です。

### シリアルデータ・フォーマット

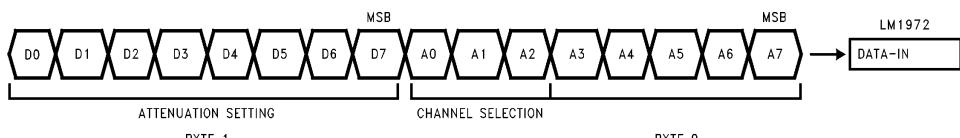

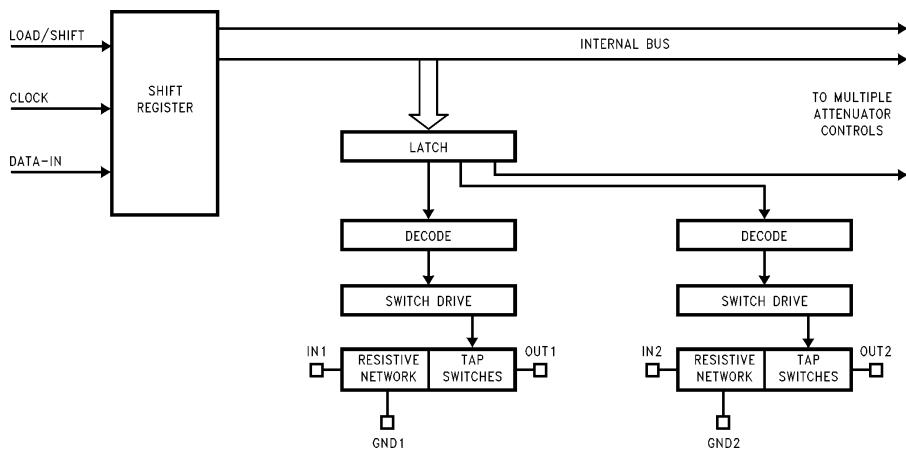

LM1972 は、マイクロ・コントローラによる制御が容易な 3 線式のシリアル・インターフェースを採用しています。Fig. 2 に、その 3 線信号 (データ入力、クロック、ロード/シフト) のタイミング図を示します。Fig. 8 のブロック図は、デジタル・インターフェースを介してタップ・スイッチを制御し、所定の減衰レベルを選択する構成を示しています。Fig. 2 のタイミング図に示されるように、ロード/シフト・ラインは、最初のクロック・パルスの立上がりエッジよりも最低 150ns 前に Low にし、16 データ・ビットのすべてが転送されるまで Low 状態に保持する必要があります。シリアル・データはチャネル選択用のビットと、それに続く減衰量設定用の 8 ビットから構成され、いずれも最初に MSB から転送します。8 ビットの減衰量設定データに先き立ち、8 ビットのアドレス・データを転送します。Fig. 7 にシリアル・データ・フォーマットの転送プロセスを示します。

TABLE I. LM1972 Micropot Attenuator Register Set Description

| MSB                       | LSB                  |

|---------------------------|----------------------|

| Address Register (Byte 0) |                      |

| 0000 0000                 | Channel 1            |

| 0000 0001                 | Channel 2            |

| 0000 0010                 | Channel 3            |

| Data Register (Byte 1)    |                      |

| Contents                  | Attenuation Level dB |

| 0000 0000                 | 0.0                  |

| 0000 0001                 | 0.5                  |

| 0000 0010                 | 1.0                  |

| 0000 0011                 | 1.5                  |

| :::::                     | ::                   |

| 0001 1110                 | 15.0                 |

| 0001 1111                 | 15.5                 |

| 0010 0000                 | 16.0                 |

| 0010 0001                 | 16.5                 |

| 0010 0010                 | 17.0                 |

| :::::                     | ::                   |

| 0101 1110                 | 47.0                 |

| 0101 1111                 | 47.5                 |

| 0110 0000                 | 48.0                 |

| 0110 0001                 | 49.0                 |

| 0110 0010                 | 50.0                 |

| :::::                     | ::                   |

| 0111 1100                 | 76.0                 |

| 0111 1101                 | 77.0                 |

| 0111 1110                 | 78.0                 |

| 0111 1111                 | 100.0 (Mute)         |

| 1000 0000                 | 100.0 (Mute)         |

| :::::                     | ::                   |

| 1111 1110                 | 100.0 (Mute)         |

| 1111 1111                 | 100.0 (Mute)         |

FIGURE 7. Serial Data Format Transfer Process

TLH/11978-10

## アプリケーション情報(つづき)

### $\mu$ Potのシステム・アーキテクチャ

$\mu$ Potのデジタル・インターフェースは本質的にはシフトレジスタであり、このインターフェースを介し、シリアル・データのシフトイン、ラッチ、デコードが行われます。新しいデータがデータ入力ピンにシフトインされると、それより前のデータはデータ出力ピンからシフトアウトされます。データのシフトイン後に、ロード/シフト・ラインがHighになり、新たなデータがラッピングされます。次に、このデータはデコードされ、該当するタップ・スイッチが切り替わり、選択されたチャネルは任意の減衰レベルに設定されます。このプロセスは、減衰量を変更する毎に繰り返されます。なお、各チャネルの減衰レベルは、アッテネーションを変更するためにチャネルを選択した時、または $\mu$ Potをパワーダウンして再度電源投入した時に限り更新されます。 $\mu$ Potを電源投入した時は、各チャネルともミュート・モードになります。

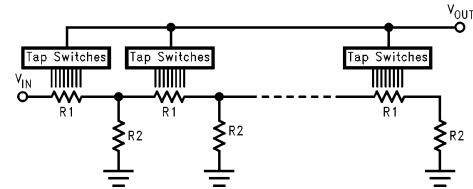

### $\mu$ Potのラダー・アーキテクチャ

$\mu$ Potの各チャネルは、それぞれ独立した抵抗ラダー・ネットワーク回路により構成されています。Fig. 9に示すように、このラダー回路は複数のR1/R2抵抗素子から構成されており、減衰レベルの設定に使用されます。各素子に内蔵されている複数のタップ・スイッチにより、Table 1のデータ・ビットに対応する減衰レベルが選択されます。Fig. 9のラダー回路からわかるように、チャネルの入力インピーダンスは選択されたタップ・スイッチに関係なく一定ですが、出力インピーダンスは選択されたタップ・スイッチによって変動します。

TL/H/11978-12

FIGURE 9.  $\mu$ Pot Ladder Architecture

### デジタル・ラインの信号レベル

$\mu$ Potのデジタル・インターフェース部は、シフトレジスタの入力が2ダイオード・ドロップ分(約1.4V)のスレッショルド電圧で動作するため、TTLまたはCMOSロジック・コンパチブルとなっています。

### デジタルデータ出力ピン

複数の $\mu$ Potのデータ出力ピンを使用し、デイジーチェーンのシステム構成することができます。デイジーチェーン構成では、各チーナン当たりデータラインとロード/シフトラインがそれぞれ1本だけで済むため、プリント基板の配線パターンを簡素化できます。

データ出力ピンを使用しない場合はチャネル間の分離を確実に行い、信号ラインにデジタルノイズが乗らないように、 $2k\Omega$ の抵抗を介してデータ出力ピンを終端して下さい。このピンをフローティング状態にしておくこともできますが、データ出力ラインの信号ノイズが隣接ラインに乗ってノイズ特性が悪化することがあります。

TL/H/11978-11

FIGURE 8.  $\mu$ Pot System Architecture

## アプリケーション情報(つづき)

### デイジーチェーン機能

$\mu$ Pot のデジタル・インターフェースは基本的にシフトレジスタですから、同じデータ・ラインとロード/シフト・ラインで複数の $\mu$ Pot をプログラムすることができます。Fig. 10 に示すように、n 個の $\mu$ Pot をデイジーチェーンで接続する場合、16 ビットがシフト、ロードされます。データのロード手順は、 $\mu$ Pot が 1 個の時と同じです。先ず、ロード/シフト・ラインが Low になり、続いてデータがクロックに同期して順番に取り込まれ、同時に各 $\mu$ Pot にある先行データがデータ出力ピンからチェーンの後続 $\mu$ Pot にシフトアウトされ行きます(チェーンの最終 $\mu$ Pot ではグランドにシフトアウト)。この後、ロード/シフト・ラインが High になり、データはそれぞれ対応する $\mu$ Pot にラッピングされます。データはアドレスに従ってデコードされ(チャネルの選択)、減衰レベルの制御を行なうタップ・スイッチが選択されます。

### クロストークの測定

$\mu$ Pot のクロストーク ("Typical Performance Characteristics" の項を参照) は、片側チャネルに信号を入力し、他チャネルの同一周波数の出力レベルを測定して求めたものです。正確なクロストークを求めるためには、同じ周波数の信号レベルで測定することが重要です。また、測定精度を上げるために、1 $\mu$ F のコンデンサを介して測定チャネル入力の AC 接地が必要です。

### クリック / ポップの防止

ここでは、3 つの理由から出力バッファの必要性について説明します。これらの理由はシステム上すべて重要です。

第 1 に、 $\mu$ Pot の出力段にバッファ / アンプを付加することで、デバイスの減衰ステップ変更により生じる可聴クリック / ポップを確実に防止することができます。出力段にオンボードのバイポーラ・オペアンプを使用している場合、 $\mu$ Pot の出力インピーダンスの変化時に、このオペアンプの動作に一定量の DC バイアス電流が必要となり、DC 電圧の "ポップ" が発生します。すなわち、 $\mu$ Pot の出力インピーダンスが減衰ステップの変化に伴って変化すると、バイポーラ・アンプ動作に一定量の DC バイアス電流が必要になり、このポップ現象が起こります。DC 電圧の "ポップ" は出力インピーダンスが変化すると、DC バイアス電流も変化するため発生します。

第 2 に、 $\mu$ Pot にドライブ機能がないため、バッファ / 非反転アンプによりゲインを獲得しなければなりません。

第 3 に、 $\mu$ Pot の出力を高インピーダンスにし、負荷がかかるると直線性誤差が生じるので防ぐ必要があるためです。JFET 入力バッファを使用すれば、 $\mu$ Pot の出力段に高入力インピーダンスが得られるので、こうした問題は生じません。

クリックとポップは、LF412ACN などの JFET 入力バッファ / アンプを使用することで防止することができます。LF412 は高入力インピーダンスだけでなく、オーディオ帯域における低ノイズ・フロア、低 THD + N を特長としているため、システムでの信号状態と直線性を確保することができます。この方法では、システム全体の性能は JFET 入力バッファ / アンプの品質と性能によって決まります。

### 対数ゲイン・アンプ

$\mu$ Pot はアンプの帰還ループで使用することもできますが、この場合も、前述したように $\mu$ Pot の出力を高インピーダンスにし、その高精度の性能と直線性を確保する必要があります。同様に、出力に負荷がかかると減衰量の値も変化します。対数ゲイン・アンプを形成する場合は、Fig. 11 に示すように $\mu$ Pot を用いて帰還ループを構成します。この構成では、Table I に示した減衰レベルがゲイン・レベルとなり、最大 78dB の増幅が可能です。ほとんどのアプリケーションでは、ゲインを 78dB になると信号クリッピングを生じますが、 $\mu$ Pot はプログラミングによりゲインの調整を行い、システムのクリッピング・レベルを回避することができます。なお、ミュート・モードでは、入力が出力から分離されることに注意して下さい。この構成でミュート・モードにすると、アンプがオープン・ループ・ゲイン状態になり、コンバレータの動作になります。こうした回路のプログラミングと設計には細心の注意が必要です。最大限の性能を得るためにには、JFET 入力アンプを使用して下さい。

TL/H/11978-14

FIGURE 11. Digitally-Controlled Logarithmic Gain Amplifier Circuit

FIGURE 10. n- $\mu$  Pot Daisy-Chained Circuit

## **NOTE**

## Physical Dimensions inches (millimeters)

Surface Mount Package

Order Number LM1972M

NS Package Number M20B

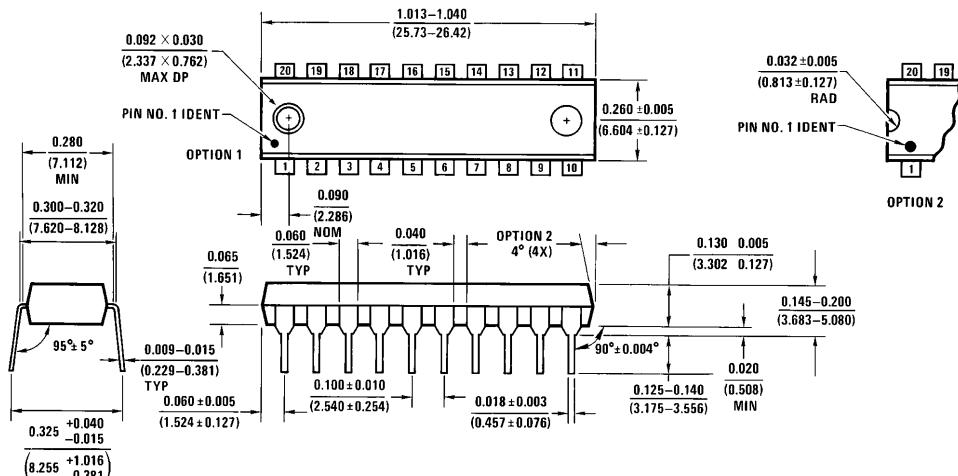

## Physical Dimensions inches (millimeters) (つづき)

N20A (REV G)

Dual-In-Line Plastic Package

Order Number LM1972N

NS Package Number N20A

## 生命維持装置への使用について

弊社の製品はナショナル セミコンダクター社の書面による許可なくしては、生命維持用の装置またはシステム内の重要な部品として使用することはできません。

1. 生命維持用の装置またはシステムとは (a) 体内に外科的に使用されることを意図されたもの、または (b) 生命を維持あるいは支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、この不具合が使用者に身体的障害を与えると予想されるものをいいります。

2. 重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいいります。

## ナショナルセミコンダクター ジャパン株式会社

本社 / 〒135-0042 東京都江東区木場 2-17-16 TEL.(03)5639-7300 <http://www.nsjk.co.jp/>

製品に関するお問い合わせはカスタマ・レスポンス・センタのフリーダイヤルまでご連絡ください。

0120-666-116

この紙は再生紙を使用しています